Direkt-Bonden

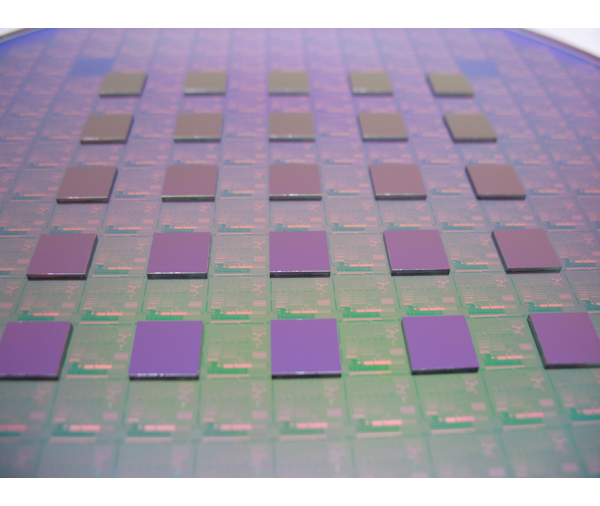

Direktes metallisches Bonden ist ein Verfahren, das verwendet wird, um zwei Komponenten zu montieren.

Trotz seiner Hauptschwierigkeit -die Anforderung von sehr hohem Reinheitsgrad-, gibt es mehrere Gründe, direktes metaliisches Bonden zu verwenden.

Die drei Hauptgründe sind: geringe Bondskraft, Raumtemperatur-Prozess und kurze Prozesszeit.

Dies alles macht direktes metallisches Bonden zu einem ernsthaften Kandidaten für Chip-Wafer Spitzentechnologien für 3D-Integration.

PROCEED-PROJEKT

2009: Start des Projekts durch Minalogic mit Unterstützung des französischen Staates (FUI - Fond Interministériel Unique).

Ziel: beweisen, eine hohe Genauigkeit der Platzierung (< 1 μm) der Chip-zu-Wafer-Strukturen durch direktes metallisches Bonden möglich ist.

In Zusammenarbeit mit CEA-Leti, ST-Microelectronics, ALES und CEMES-CNRS konnte SET dank eines speziell entwickelten FC300 die Macharbeit des direkten metallischen Bondes erfolgreich demonstrieren. Dieser Erfolg war Gegenstand zalhreicher Artikel.

IRT Nanoelec

Ende 2015 entwickelte SET zusammen mit IRT Nanoelec eine präzise und schnelle Maschine im Direktverbindungsverfahren.

SET nutzte die Erfahrungen des PROCEED-Projekts und entwirfte und entwickelte NEO HB, das sich speziell der direkten Verklebung für die Produktion widmet.

Im September 2019 brachte SET NEO HB auf der SEMICON Taiwan kommerziell auf den Markt und erfüllte damit die hohen Durchsatzanforderungen, die für die weit verbreitete Einführung der 3D-Integration erforderlich sind.

PROCEED Project

Das Projekt PROCEED von Minalogic ist ein Projekt für 4,2 Millionen Euro, 24 Monate, das von französischem FIU (Fond Interministeriel Unique) unterstützt wurde. Das Projekt begann im Jahr 2009, das Ziel des Projekts PROCEED ist, hohe Genauigkeit der Ausrichtung (< 1 μm) der Chip-zu-Wafer-Strukturen durch direktes metallisches Bonden zu beweisen. Solche Strukturen sind für 3D-Zusammenschaltungen mit Hochleistung erforderlich und ermöglichen eine Vielzahl von Anwendungen in der Mikroelektronik, sowie in Optoelektronik oder MEMS.

Direktes Kupfer-zu-Kupfer-Bonden erfordert gute Ebenheit und hervorragende Oberflächenqualität, vor allem in Bezug auf Feinstaub und metallische Verunreinigungen. Die geringe Rauigkeit von Säulen und Pads aus Kupfer, sowie die Topografie zwischen Kupfer und Oxidstellen sind entscheidend, um gute Haftfestigkeit bei geringer Kraft und Raumtemperatur zu erhalten.

Das auf Chip-zu-Wafer basierende Verfahren von direktem metallischem Bonden ist bei CEA-Leti entwickelt, um gewisse Einschränkungen in 3D-Integration zu überwinden. Diese Technologie besteht aus Chips, die auf einem Substrat bei niedriger Temperatur und Kraft angebracht werden, die das Bonden mit hoher mechanischer und elektrischer Integrität durch örtliches metallisches Bonden erstellen.

ALES versorgt Technologie, um die Vorbereitung der Oberfläche zu unterstützen, während CEMES-CNRS die Bonden-Qualität charakterisiert und Veränderungen der Kupfer-Metallurgie beim Ausglühen analysiert. STMicroelectronics führt die Anwendung dieser Technologie für die 3D-Integration mit hoher Dichte durch.

Vorteile der Technologie

Diese direkte Technologie von Metall-zu-Metall-Bonden bietet viele Vorteile im Vergleich zu herkömmlichem Bonden mit Thermokompression.

Der Bonden-Prozess erfolgt bei geringer Kraft und Raumtemperatur, ermöglicht höhere Genauigkeit von Bonden für hochdichte Zusammenschaltungen unter Umgehung der Wärmeausdehnung von unterschiedlichen Materialien. Um lückenfreies Bonden zu gewährleisten, müssen die Ausrichtung- und die Bonden-Schritte in einer partikelfreien Umgebung stattfinden. Es geschieht durch die Verwendung von speziellen Materialien und sorgfältigen Umgang mit der Bonden-Umwelt, die Wafer-Oberfläche zu schützen, während sie mit Würfeln vollständig gefüllt ist.

Ein Bonden-Prozess mit geringer Kraft ist wichtig für die hohe Durchsatzleistung, die für die weit verbreitete Annahme der IC mit 3D-Integration erforderlich ist.

Technische Dokumente

|

|

|

|

|

Chip-to-Wafer Technologies for High Density 3D Integration |

Mai 2011 |

CEA Leti Minatec, ALES, STMicroelectronics, CNRS-CEMES, SET |