RF Applications

While radio frequency devices have typically not required high accuracy bonding, some recent applications have pointed out the need for finer control of the bonding process.

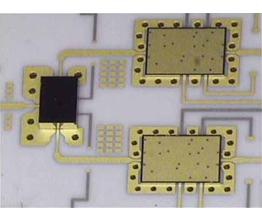

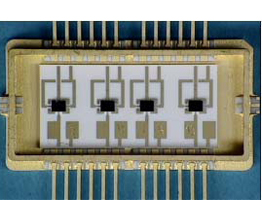

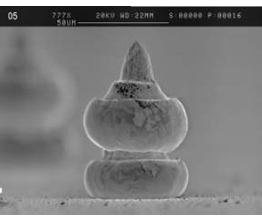

For certain RF applications such as advanced satellite systems, highly accurate alignment - within 1 µm between chip and substrate - has become desirable. The typical gold-to-gold bonding technique used for RF devices requires inordinately high force at high temperature - a combination that doesn't ordinarily lend itself to high accuracy.

SET Flip Chip Bonders will handle brittle materials safely & easily, even at elevated temperature and high force, while improved control of the force profile throughout the cycle results in better bonding accuracy. Through high performance thermo-compression and leveling capability, SET has made high-end RF connections a reality, with accuracy levels that set a new standard for RF applications.