MCM & LCD

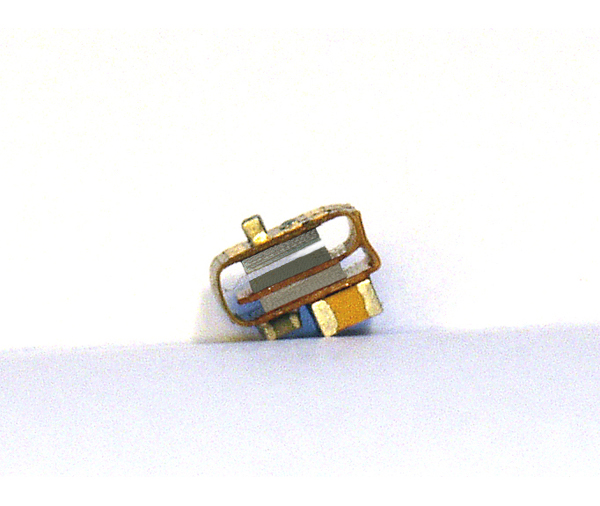

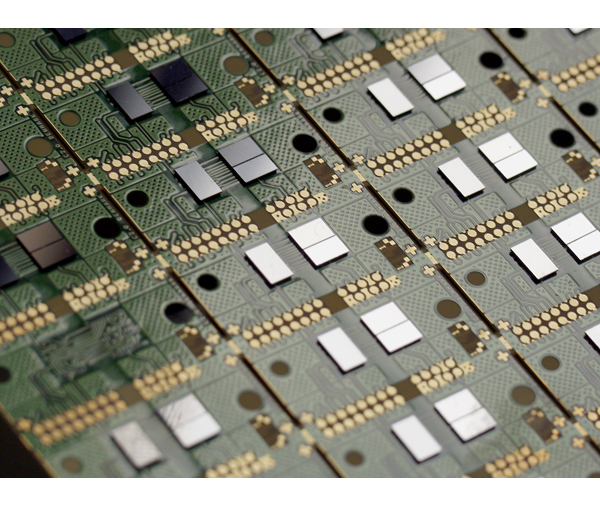

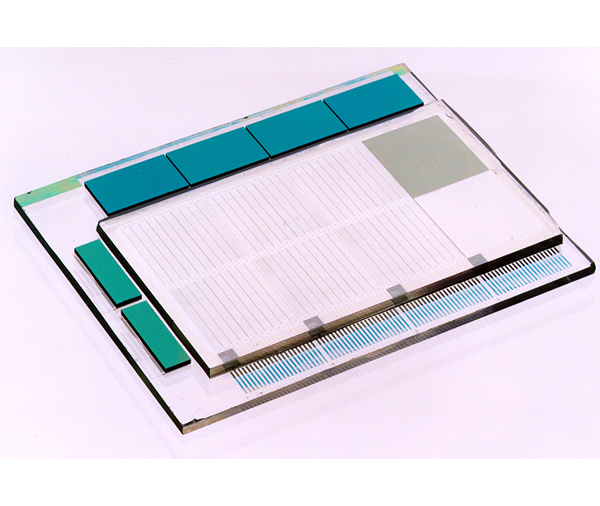

The versatility of SET's Flip-Chip Bonders has proven to be a valuable asset in creating high accuracy alignment levels for multichip modules, compound devices and LCD displays.

Standard MCM applications such as automotive electronics and computers, and LCD/chip-on-glass applications for watches, telephones and other read-out displays have been largely perfected with current flip- chip technology.

Bonding Process

Features such as a flexible user interface, auto alignment capability, and automatic tool exchange enable high-end flip chip bonding applications with maximum ease.

SET's Flip Chip Bonders have process mixing capabilities that allow multiple bonding processes within a single cycle. This provides unsurpassed flip-chip bonding flexibility in a multichip environment with different sized chips in the same cycle.