3D Interconnect

Shorten connections lengths to reduce electrical resistance, improve response time as well as reduce power consumption and overall dimensions is one of the main goal to 3D integration.

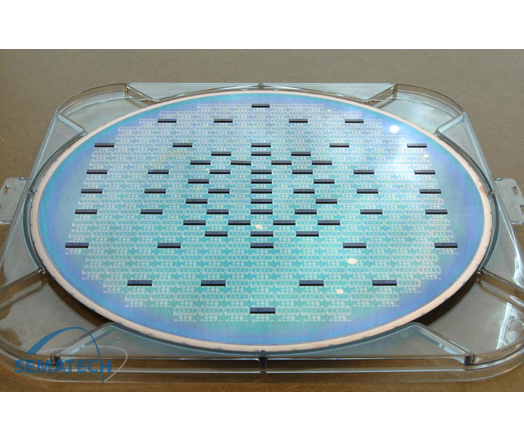

3D-IC integration enables the high yielding assembly of heterogeneous devices. There are numerous 3D packaging solutions such as:

- interposer,

- direct chip-to-chip bonding or die-to-die bonding,

- chip-to-wafer interconnection.

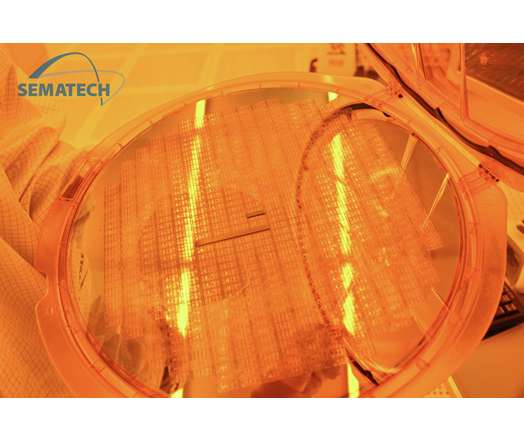

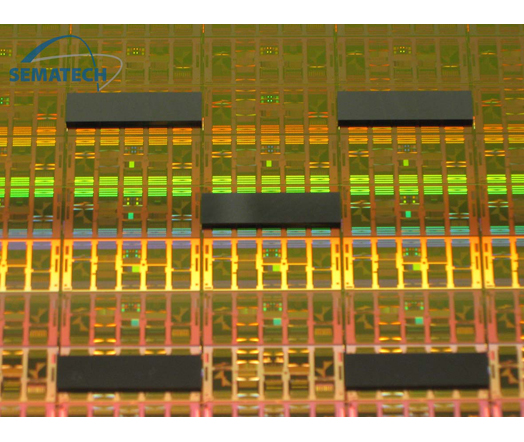

The placement accuracy requirement varies with the application and the method used to get the signal out of each die. Through-Silicon-Via (TSV) interconnection between chip layers is the focus of the industry today. The optimization of the TSV diameter and pitch is pushing the demands for higher placement accuracy, not only along X and Y axes, but also parallelism between chips.

Bonding Process

High post-bond accuracy and good parallelism between each layer are crucial parameters for 3D stacking. Several bonding processes more dedicated to 3D integration are available on SET’s Flip-Chip Bonders like :

- In-Situ reflow,

- Thermocompression

- Adhesive joining

- Direct metallic bonding

- Etc…